*=============Infinite_Bandwidth_SR_FlipFlop==================

In theory, timing should not be an issue with Set_Reset flip-flops.

=======================================================================

FF_SET_RESET

* _______

* ___| S Q |__

* | |

* ___| RS NQ|__

* |_______|

*

VCC VCC 0 DC 5

VA A 0 DC 0 PULSE( 0 5 -.5n 90p 90p 1n 4n )

VB B 0 DC 0 PULSE( 0 5 1.5n 90p 90p 1n 4n )

*VA A 0 DC 0 PULSE( 0 5 1p 90p 90p 1n 4n )

*VB B 0 DC 0 PULSE( 0 5 2n 90p 90p 1n 4n )

X_FFSRR A B VQ1 VNQ1 VCC RSFFR

X_FFSRB A B VQ2 VNQ2 VCC RSFFB1

=======================================================================

The assumption is that only the S or R input goes high

one at a time. NOR gate are being used. So that when

both S and R are low, the output NQ controls XNOR1 and

the output Q controls XNOR2. If Q happens to be low, then

raising S to high will cause NQ to go low. This provide

two low inputs to XNOR1 causing its output Q to go high.

Output Q will stay high and remain there when S goes low.

*=========RSFF_Real===========================================

* ___ ____

* |R |___\ \ ___ Don't set R and S at same time

* |___| | 1 \/\_______|Q |

* ___| /\/ | |___| ___ _______ ___

* | /___/ | |S |_| S Q |_|Q |

* |__________/|\_ |___| | | |___|

* ____________| | ___ | | ___

* | ____ | |R |_| R NQ|_|NQ |

* |_\ \ | ___ |___| |_______| |___|

* ___ | 2 \/\_____|_|NQ |

* |S |____| /\/ |___|

* |___| /___/

*

.SUBCKT RSFFR S R Q NQ VCC

XNOR1 R NQ Q VCC NOR

XNOR2 S Q NQ VCC NOR

.ENDS RSFFR

=======================================================================

As long as all the inputs are stationary at either a one

or zero at time zero, a transient analysis can start up

a behaviorally defined flip-flop.

*=========RS_FF_Behaviour_1====================================

* ___ ____

* |R |___\ \ Q ___ Convergent needs 100ps delay

* |___| | 1 \/\_______|Q | If an input moving at startup

* ___| /\/ | |___| ___ _______ ___

* | /___/ | |S |_| S Q |_|Q |

* |__________/|\_ |___| | | |___|

* ____________| | ___ | | ___

* | ____ | |R |_| R NQ|_|NQ |

* |_\ \ NQ | ___ |___| |_______| |___|

* ___ | 2 \/\_____|_|NQ |

* |S |____| /\/ |___|

* |___| /___/

*

.SUBCKT RSFFB1 S R Q NQ VCC

BNOR1 Q 0 V = 5-5*u( u(v(R )-2.5) + u(v(NQ )-2.5 ) -.1 )

BNOR2 NQ 0 V = 5-5*u( u(v(S )-2.5) + u(v(Q ) -2.5 ) -.1 )

.ENDS RSFFB1

=======================================================================

But if care is not taken to make sure the input are

not moving at time zero, a simple behavioral flip-flop

will fail to converge.

Circuit: FF_SET_RESET

Error: Timestep too small.

Error: run simulation(s) aborted.

=======================================================================

This problem can be corrected by making an infinite bandwidth

flip-flop look like a real flip-flop. Namely, bandwidth needs

to be added. By adding a 100ps delay to the outputs, the

behavioral flip-flop will converge just like a real

flip-flop.

*=========RS_FF_Behaviour_2===========================================

* ___ ____

* |R |___\ \ Q0 ____ ___ Convergent needs 100ps delay

* |___| | 1 \/\__|DLAY|______|Q | If an input moving at startup

* ___| /\/ |____| | |___| ___ _______ ___

* | /___/ | |S |_| S Q |_|Q |

* |_________________/|\_ |___| | | |___|

* ___________________| | ___ | | ___

* | ____ | |R |_| R NQ|_|NQ |

* |_\ \ NQ0 ____ | ___ |___| |_______| |___|

* ___ | 2 \/\__|DLAY|____|_|NQ |

* |S |____| /\/ |____| |___|

* |___| /___/

*

.SUBCKT RSFFB2 S R Q NQ VCC

BNOR1 Q0 0 V = 5-5*u( u(v(R )-2.5) + u(v(NQ )-2.5 ) -.1 )

BNOR2 NQ0 0 V = 5-5*u( u(v(S )-2.5) + u(v(Q ) -2.5 ) -.1 )

XDLAYQ Q0 Q VCC TAU

XDLAYNQ NQ0 NQ VCC TAU

.ENDS RSFFB2

*=========Delay_100ps===========================================

* ___

* _/\ /\ /\_____ ____|OUT|

* | \/ \/ | | | |___|

* ___ _|_ RLP _|_ | _|_

* |IN |_/BUF\ ___ |_/OUY\

* |___| \___/ CLP | \___/

* _|_ _|_ _|_

* /// /// ///

*

*

.SUBCKT TAU IN OUT VCC

BBUF VIN 0 V = 5-5*u( v(IN )-2.5 )

RLP VIN VLP 1K

CLP VLP 0 100f

BOUT OUT 0 V = 5-5*u( v(VLP )-2.5 )

.ENDS TAU

=======================================================================

The delay is in effect delaying the regeneration process of BNOR1

and BNOR2 at time zero. The real flip-flop does this automatically.

Since both BNOR1 and BNOR2 are in feedback with each other,

infinite bandwidth, infinite gain, and moving inputs might explain

why Spice is having a little trouble converging.

In the case of a binary counter, the convergence problem can't be

solved by just making sure all inputs are stationary at time

zero.

===========Full_Netlist_For_Copy_Paste=======================

FF_SET_RESET

* _______

* ___| S Q |__

* | |

* ___| RS NQ|__

* |_______|

*

*.OPTIONS GMIN=1e-18 METHOD=traps

VCC VCC 0 DC 5

VA A 0 DC 0 PULSE( 0 5 -.5n 90p 90p 1n 4n )

VB B 0 DC 0 PULSE( 0 5 1.5n 90p 90p 1n 4n )

*VA A 0 DC 0 PULSE( 0 5 1p 90p 90p 1n 4n )

*VB B 0 DC 0 PULSE( 0 5 2n 90p 90p 1n 4n )

X_FFSRR A B VQ1 VNQ1 VCC RSFFR

X_FFSRB A B VQ2 VNQ2 VCC RSFFB1

*TRAN TSTEP TSTOP TSTART TMAX ?UIC?

.tran 10p 10n 0 10p UIC

*=========Run_Sim============================================

.control

run

set pensize = 2

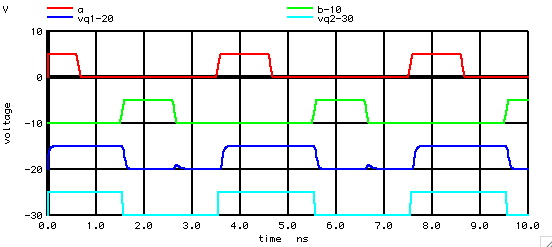

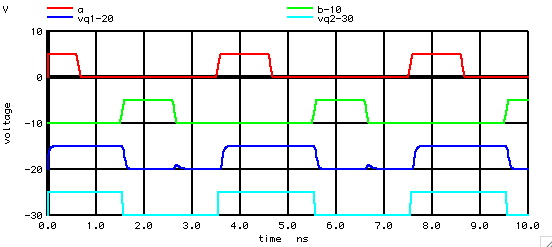

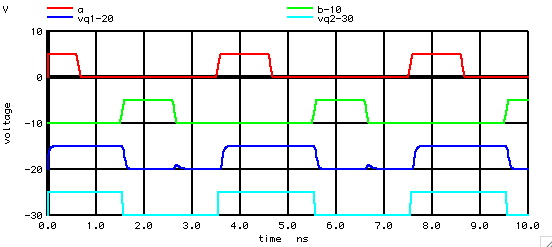

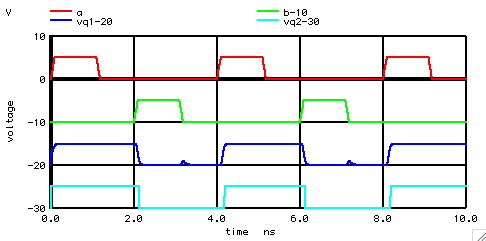

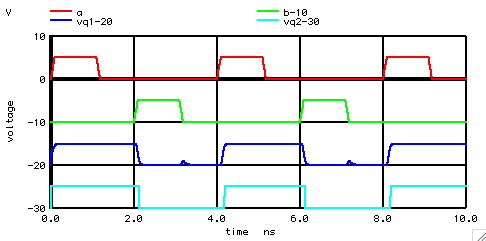

plot a b-10 vq1-20 vq2-30

.endc

*=========The_CMOS_Model_Files==================================

.model NMOSC NMOS(Level= 1 Cbs=2f Cbd=2f)

.model PMOSC PMOS(Level= 1 Cbs=2f Cbd=2f)

*=========RS_FF_Behaviour_1===========================================

* ___ ____

* |R |___\ \ Q0 ____ ___ Convergent needs 100ps delay

* |___| | 1 \/\__|DLAY|______|Q | If an input moving at startup

* ___| /\/ |____| | |___| ___ _______ ___

* | /___/ | |S |_| S Q |_|Q |

* |_________________/|\_ |___| | | |___|

* ___________________| | ___ | | ___

* | ____ | |R |_| R NQ|_|NQ |

* |_\ \ NQ0 ____ | ___ |___| |_______| |___|

* ___ | 2 \/\__|DLAY|____|_|NQ |

* |S |____| /\/ |____| |___|

* |___| /___/

*

.SUBCKT RSFFB1 S R Q NQ VCC

BNOR1 Q 0 V = 5-5*u( u(v(R )-2.5) + u(v(NQ )-2.5 ) -.1 )

BNOR2 NQ 0 V = 5-5*u( u(v(S )-2.5) + u(v(Q ) -2.5 ) -.1 )

.ENDS RSFFB1

*=========RS_FF_Behaviour_2===========================================

* ___ ____

* |R |___\ \ Q0 ____ ___ Convergent needs 100ps delay

* |___| | 1 \/\__|DLAY|______|Q | If an input moving at startup

* ___| /\/ |____| | |___| ___ _______ ___

* | /___/ | |S |_| S Q |_|Q |

* |_________________/|\_ |___| | | |___|

* ___________________| | ___ | | ___

* | ____ | |R |_| R NQ|_|NQ |

* |_\ \ NQ0 ____ | ___ |___| |_______| |___|

* ___ | 2 \/\__|DLAY|____|_|NQ |

* |S |____| /\/ |____| |___|

* |___| /___/

*

.SUBCKT RSFFB2 S R Q NQ VCC

BNOR1 Q0 0 V = 5-5*u( u(v(R )-2.5) + u(v(NQ )-2.5 ) -.1 )

BNOR2 NQ0 0 V = 5-5*u( u(v(S )-2.5) + u(v(Q ) -2.5 ) -.1 )

XDLAYQ Q0 Q VCC TAU

XDLAYNQ NQ0 NQ VCC TAU

.ENDS RSFFB2

*=========Delay_100ps===========================================

* ___

* _/\ /\ /\_____ ____|OUT|

* | \/ \/ | | | |___|

* ___ _|_ RLP _|_ | _|_

* |IN |_/BUF\ ___ |_/OUY\

* |___| \___/ CLP | \___/

* _|_ _|_ _|_

* /// /// ///

*

*

.SUBCKT TAU IN OUT VCC

BBUF VIN 0 V = 5-5*u( v(IN )-2.5 )

RLP VIN VLP 1K

CLP VLP 0 100f

BOUT OUT 0 V = 5-5*u( v(VLP )-2.5 )

.ENDS TAU

*=========RSFF_Real===========================================

* ___ ____

* |R |___\ \ ___

* |___| | 1 \/\_______|Q |

* ___| /\/ | |___| ___ _______ ___

* | /___/ | |S |_| S Q |_|Q |

* |__________/|\_ |___| | | |___|

* ____________| | ___ | | ___

* | ____ | |R |_| R NQ|_|NQ |

* |_\ \ | ___ |___| |_______| |___|

* ___ | 2 \/\_____|_|NQ |

* |S |____| /\/ |___|

* |___| /___/

*

.SUBCKT RSFFR S R Q NQ VCC

XNOR1 R NQ Q VCC NOR

XNOR2 S Q NQ VCC NOR

.ENDS RSFFR

*=========NOR============================================

* ^

* /_\ VCC

* |

* ||<- XNOR A B OUT VCC NOR

* __________||MP1

* | ||__ ^ VCC

* | | V2 ___ /_\

* ___ | ||<- ___ \ \_|

* |A |_/|\_________||MP2 ___ |A |__\ \ _ ___

* |___| | | ||_____|OUT| |___| | \/ \_|OUT|

* | | | |___| ___ |NOR /\_/ |___|

* | __/|\____| |B |__/ /

* | __| | __| |___| /___/

* ___ | || | ||

* |B |__|_|| MN1 |_|| MN2

* |___| ||-> ||->

* _|_ _|_

* /// ///

.SUBCKT NOR A B OUT VCC

MN1 OUT B 0 0 NMOSC W=1u L=1u

MN2 OUT A 0 0 NMOSC W=1u L=1u

MP1 V2 B VCC VCC PMOSC W=3u L=1u

MP2 OUT A V2 VCC PMOSC W=3u L=1u

.ENDS NOR

.end